39 phase locked loop block diagram

4 CD4046B Phase-Locked Loop: A Versatile Building Block for Micropower Digital and Analog Applications 3 CD4046B PLL Technical Description Figure 2 shows a block diagram of the CD4046B, which has been implemented on a single monolithic integrated circuit. The PLL structure consists of a low-power, linear VCO and two A phase-locked loop or phase lock loop (PLL) is a control system that generates an output signal whose phase is related to the phase of an input signal. There are several different types; the simplest is an electronic circuit consisting of a variable frequency oscillator and a phase detector in a feedback loop.The oscillator generates a periodic signal, and the phase detector compares the ...

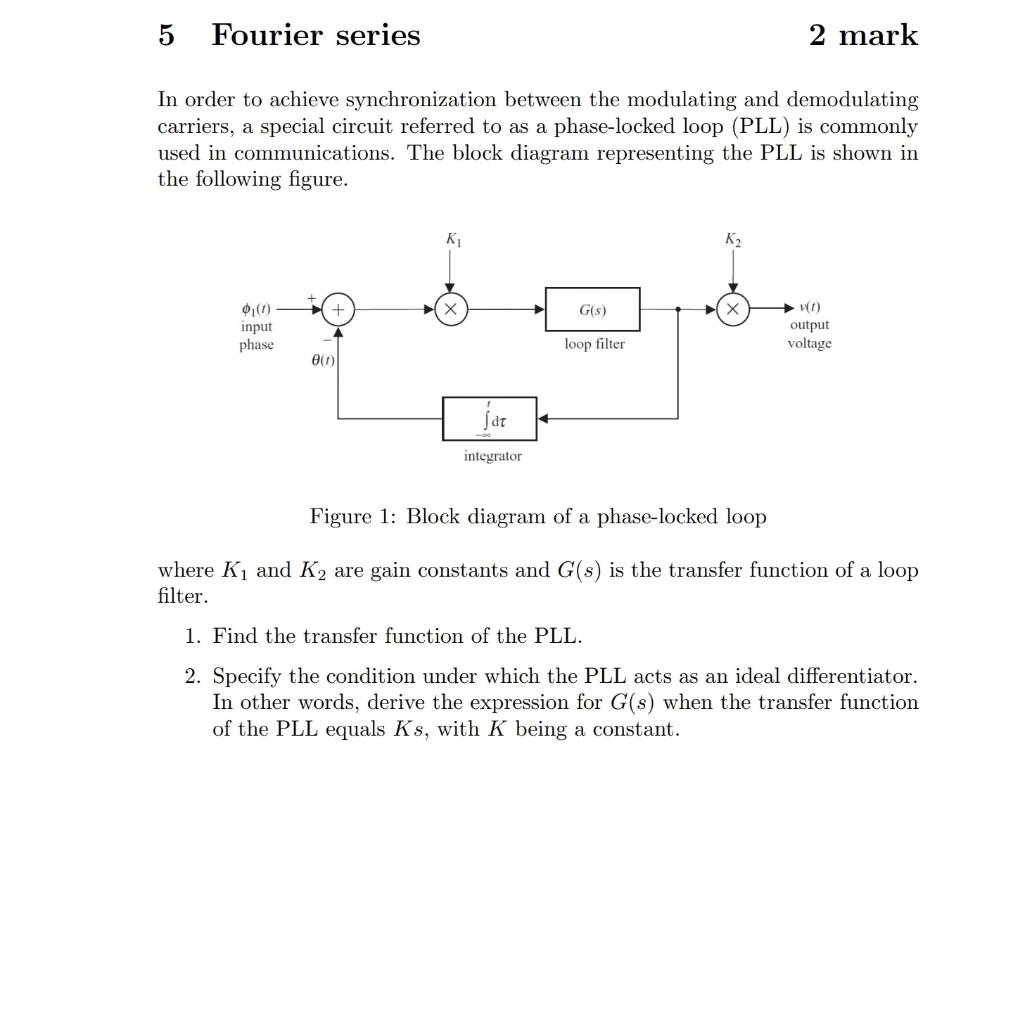

Introduction to phase-locked loop system modeling Introduction Phase-locked loops (PLLs) are one of the basic building blocks in modern electronic systems. They have been widely used in com-munications, multimedia and many other applications. The theory and mathematical models used to describe PLLs are of two types: linear and nonlinear ...

Phase locked loop block diagram

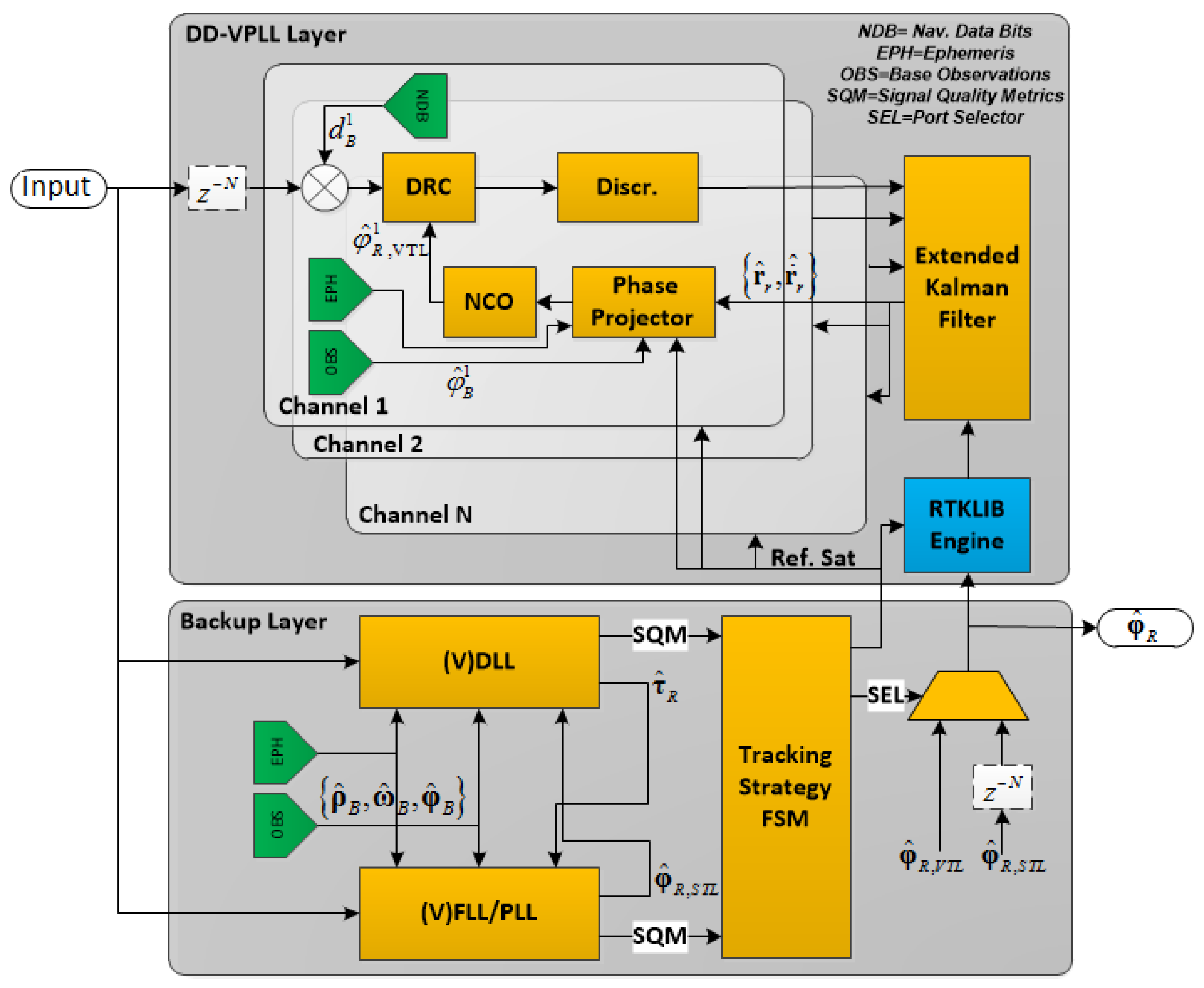

C. Three-phase PLL design A block diagram displaying the functional components of a generic PLL is shown in Figure 3. For small deviations, standard simplifying assumptions [7] allow the PLL to be modeled according to the linear block diagram of Figure 4, where t is the phase of the measured voltage and p is the phase estimate given by the PLL. This block diagram (and detailed discussion, including SPICE model for closed-loop, time-domain simulations) provide the basic feedback view of operation of the Phase-Locked Loop (PLL) Starting from the input side, the "phase comparator" is the "summing node" (from OpAmp terminology) which generates an The Phase Locked Loop concept was first developed in 1930. Since then it is used in communication systems of different types, particularly in satellite communication system. Before the invention of IC PLL, systems were very complex and costly for use in most consumer & industrial systems.

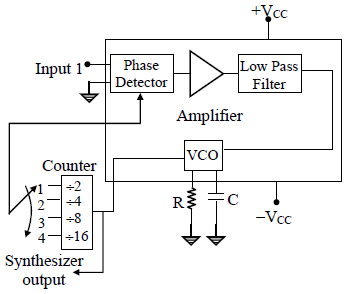

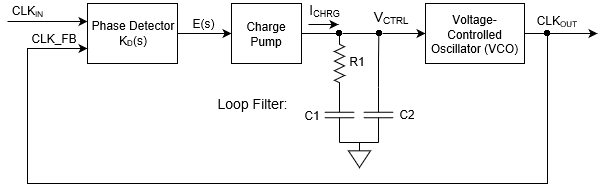

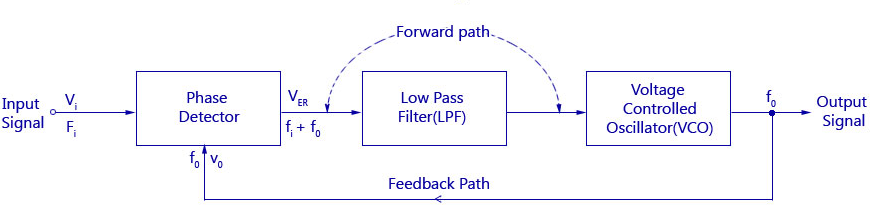

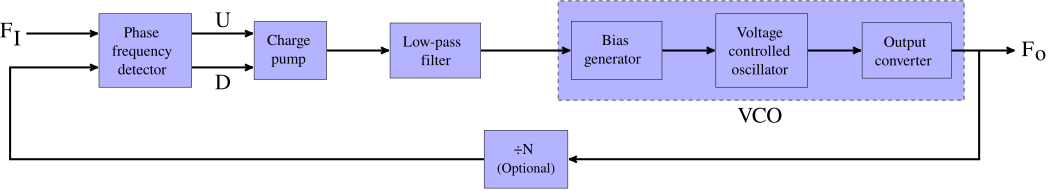

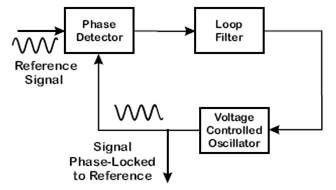

Phase locked loop block diagram. Range of input signal frequencies over which the loop remains locked once it has captured the input signal. This can be limited either by the phase detector or the VCO frequency range. a. If limited by phase detector: π/2 π φ KDπ/2-KDπ/2 Ve 0 < φ < π is the active range where lock can be maintained. For the phase detector type Phase-Locked Loops • Applications: Frequency synthesizer, TV, Demodulators, clock recovery circuits, multipliers, etc. • Basic Idea: A negative feedback control system • Basic Components: PD, Loop Filter (LPF), VCO • Types: Analog / Digital • Operation: when it is locked it will track the input frequency: w out=w in Mixer The phase locked loop or PLL is an electronic circuit with a voltage controlled oscillator, whose output frequency is continuously adjusted according to the input signal's frequency. A Phase locked loop is used for tracking phase and frequency of the input signal. It is a very useful device for synchronous communication. Phase Locked Loop. Phase Locked Loops (PLLs) are feedback control circuits that lock on to the frequency and phase of the input signal and produce an output signal with frequency and phase that is proportional to that of the input. Below is a block diagram of an analog PLL based on a device called a charge pump, which can generate a voltage ...

Block Diagram of an ADPLL Digital Phase Detector Digital Loop Filter Digital VCO v1 v2' "vd" "vf" Square Waves ... N before M Loop Filter Block diagram: v1 v2' PFD ... When the loop is locked, fc = MNf1. Note that the duration of the start pulse < 1/fc. Waveforms: Phase-Locked Loop (PLL) A PLL is a negative feedback system where an oscillator-generated signal is phase and frequency locked to a reference signal. Typical applications of PLL are: Frequency Synthesis (e.g. generating a 1 GHz clock from a 50 MHz reference) Clock Deskewing (e.g. phase-aligning an internal clock to an output clock to external device) Extracting […] IEEE Press, 1996. Design," PHASE LOCKED LOOP (Design and Implementation) A Project Report submitted by SNEHIL VERMA (14700) in partial fulfilment of the requirements for the award of the degree of ... Figure 1.1: Block Diagram The basic structure of the PLL can be understood from the block diagram above.

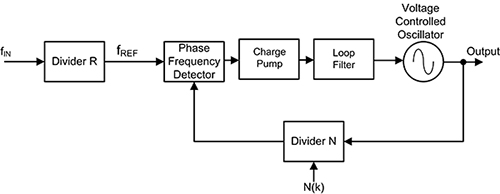

In this video, i have explained Phase Lock Loop by following outlines:1. Phase Lock Loop2. Basics of Phase Lock Loop3. Need of Phase Lock Loop 4. Block Diagr... The block diagram of a phase locked loop. (11.35) f ref = f d = F out N. or (11.36) F out = N f ref. Since the divisor N is easy to change in practice, a wide range of frequencies can be generated from a single reference. These frequencies have the accuracy and long-term stability of the original reference. Describe the basic block diagram of the phase locked loop (PLL). A phase locked loop is basically a closed loop system designed to lock the output frequency and phase to the frequency and phase of an input signal. They are used in applications such as frequency synthesis, frequency modulation/demodulation, AM detection, tracking filters, FSK ... The block diagram of a phase locked loop. (11.35) f ref = f d = F out N. or (11.36) F out = N f ref. Since the divisor N is easy to change in practice, a wide range of frequencies can be generated from a single reference. These frequencies have the accuracy and long-term stability of the original reference.

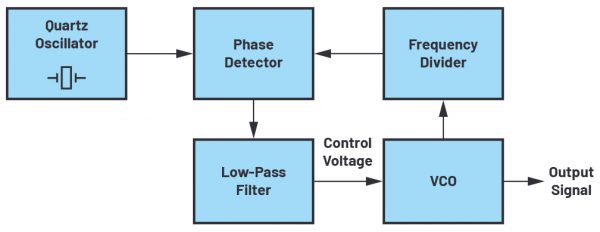

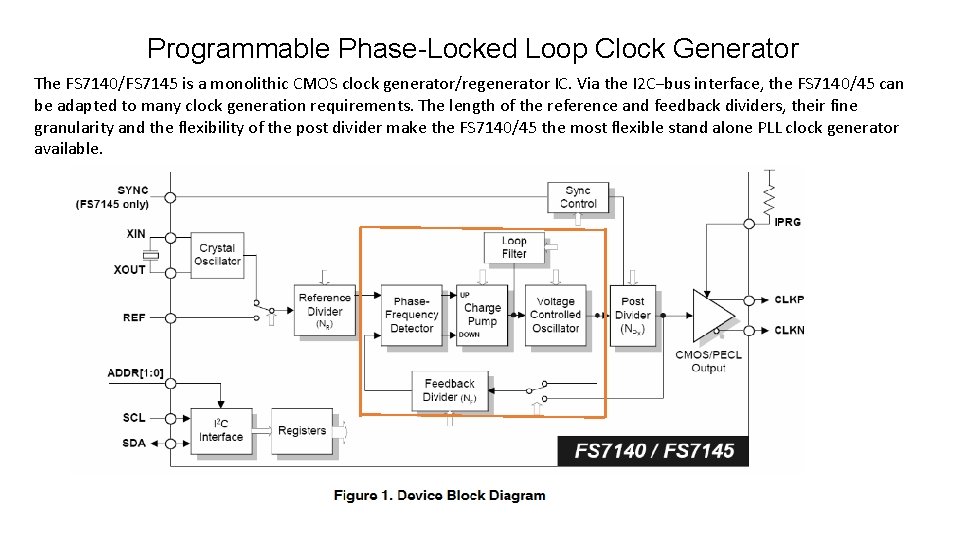

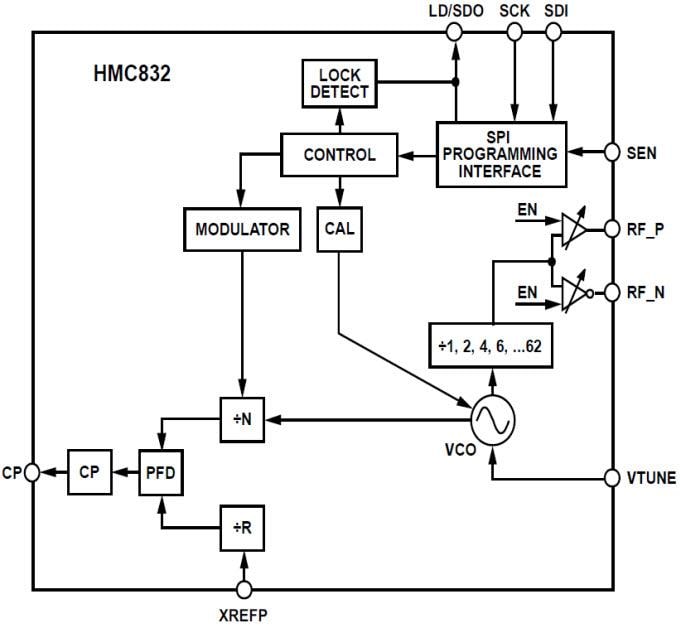

... phase locked Loop (PLL) is then used to lock the VCO. The typical PLL block diagram as in figure 2 shows a crystal oscillator frequency divided by R to ...

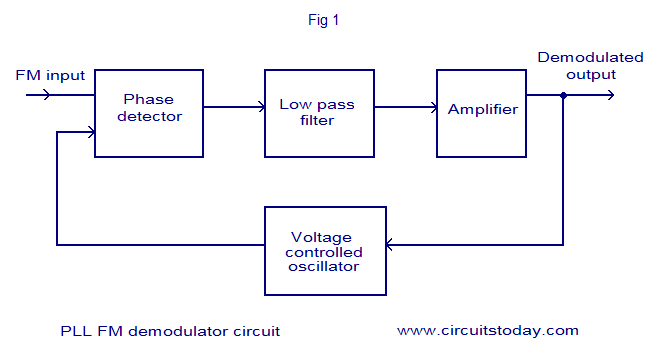

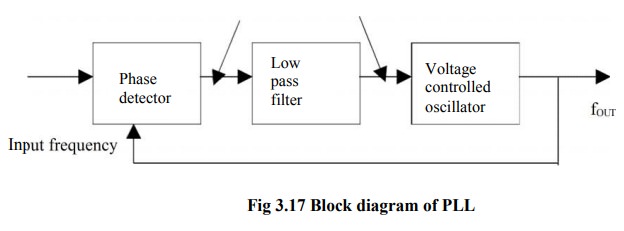

PLL Block Diagram. The block diagram of a basic PLL is shown in the figure below. It is basically a flip flop consisting of a phase detector, a low pass filter (LPF),and a Voltage Controlled Oscillator (VCO). Block Diagram - Phase Locked Loops

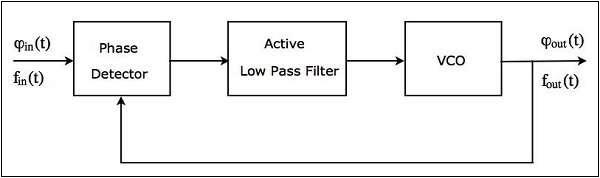

scale:0.85 Continuous time analog phase-locked loop block diagram [ analog_pll_diagram ] depicts a simplified continuous-time analog PLL. We can think of the input to the system as being an unknown phase \(\phi\) , possibly corrupted by noise, while the output of is an estimate of this phase, \(\hat{\phi}\) .

In this video i have explainedIntroduction of phase lock loop in hindi. working of phase lock loop. What is Phase Lock Loop (PLL)? How Phase Lock Loop Works....

Block Diagram And Working Principle Of PLL. The phase-locked loop consists of a phase detector, a voltage controlled oscillator and, in between them, a low pass filter is fixed. The input signal 'Vi' with an input frequency 'Fi' is conceded by a phase detector. Basically the phase detector is a comparator that compares the input ...

The digital phase-locked-loop block diagram of a magnetic hard-disk read channel shown on F ig.1 is referred to the paper presented by T oshio Murayam a in 1996 [2]. 8. Fig.1 Magnetic hard-disk read channel diagram By means of the Verilog-A hardware description language, the behavior

Block diagram: x(t) PFD QA QB VDD Cp I1 I2 S1 S2 VCO y(t) Fig. 2.2-20 The charge pump and capacitor Cp serve as the loop filter for the PLL. The charge pump can provide infinite gain for a static phase shift.

Phase Locked Loop System Block Diagram. The figure shows the block diagram of the phase locked loop system in FM transmitter that consists of different blocks such as a crystal oscillator, phase detector, loop filter, voltage controlled oscillator (VCO), and frequency divider.

A Phase Locked Loop (PLL) is a device used to synchronize a periodic waveform with a reference periodic waveform. It is an automatic control system in which the phase of the output signal is locked to the phase of the input reference signal. In the context of carrier phase synchronization, we talk about tracking the phase of an input reference ...

Block Diagram Electronic Circuit Analog To Digital Converter Circuit Diagram Phase Locked Loop Analog Circuits Electronics Text Png Pngegg

The phase locked loop or PLL is a particularly useful circuit block that is widely used in radio frequency or wireless applications. In view of its usefulness, the phase locked loop or PLL is found in many wireless, radio, and general electronic items from mobile phones to broadcast radios, televisions to Wi-Fi routers, walkie talkie radios to professional communications systems and vey much more.

The Block Diagram Of A Frequency Synthesizer Consisting Of Phase Locked Loop Pll And Adivide By N Counter Comprising 2 4 8 16 Outputs Is Sketched Below The Synthesizer Isexcited With A 5 Khz

Phase Locked Loop (PLL) is one of the vital blocks in linear systems. It is useful in communication systems such as radars, satellites, FMs, etc. This chapter discusses about the block diagram of PLL and IC 565 in detail. Block Diagram of PLL. A Phase Locked Loop (PLL) mainly consists of the following three blocks −. Phase Detector; Active ...

Phase Locked Loop Block Diagram!" ÖN Ref Div Loop Filter VCO Phase Locked Loops (PLL) are ubiquitous circuits used in countless communication and engineering applications. Components include a VCO, a frequency divider, a phase detector (PD), and a loop lter. Niknejad PLLs and Frequency Synthesis

The Phase Locked Loop concept was first developed in 1930. Since then it is used in communication systems of different types, particularly in satellite communication system. Before the invention of IC PLL, systems were very complex and costly for use in most consumer & industrial systems.

This block diagram (and detailed discussion, including SPICE model for closed-loop, time-domain simulations) provide the basic feedback view of operation of the Phase-Locked Loop (PLL) Starting from the input side, the "phase comparator" is the "summing node" (from OpAmp terminology) which generates an

C. Three-phase PLL design A block diagram displaying the functional components of a generic PLL is shown in Figure 3. For small deviations, standard simplifying assumptions [7] allow the PLL to be modeled according to the linear block diagram of Figure 4, where t is the phase of the measured voltage and p is the phase estimate given by the PLL.

Optical Phase Locking Techniques An Overview And A Novel Method Based On Single Side Sub Carrier Modulation

0 Response to "39 phase locked loop block diagram"

Post a Comment